amd 第五代 epyc“都灵”cpu 曝光|amd|第五代-爱游戏app官网入口

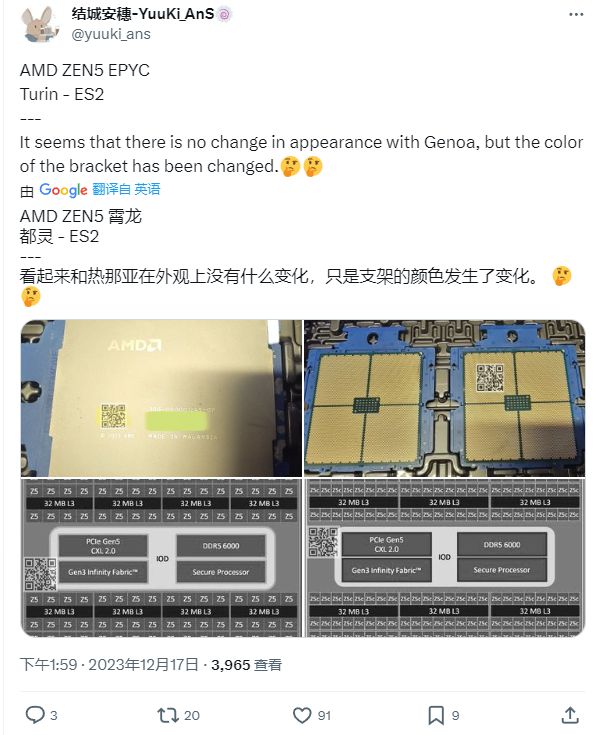

it之家 12 月 17 日消息,@结城安穗-yuuki_ans 放出了基于 zen5 架构的 amdepyc 处理器 ——

都灵(turin)的照片。

从图来看,这一代处理器设计变化不大,相比genoa 几乎没有太大变化,只是支架的颜色发生了改变预计,将会与sp5 平台保持兼容性。

该系列处理器最多有 16 个 ccd,每个 ccd 带有 8 个物理核心以及独立的 32 mb l3 缓存,最多128 个核心和 256 个线程以及512 mb 的 l3 缓存。与基于 zen 4 的 genoa 系列 cpu 相比,该系列处理器增加了 33% 的核心数量以及33% 的 l3 缓存。

此外,该系列处理器 iod 将采用支持 6000 mt/s 速度的 ddr5 集成内存控制器,以及 pcie gen5 (cxl 2.0)、gen3 infinity fabric 和安全处理器支持以及一系列其他控制器和加速器。

都灵属于 amd 第五代 epyc 产品线,将用来取代当前第四代 epyc 家族产品(genoa、genoa-x、bergamo 和 siena)。考虑到第四代 epyc 处理器(9004/8004)使用了 zen 4 zen 4c 混合架构,而第五代 epyc 也将采用类似的 zen 5(nirvana) zen 5c(prometheus)设计。

从 @结城安穗-yuuki_ans 给出的图片来看,这颗都灵 es2 芯片生产于 2023 年,看起来非常新。

实际上,@ditto_55 上个月已经给出了该系列处理器(内部代号为 breithorn)的 opn 代码,it之家汇总如下:

100-000001245 -16 ccd 1 iod(128 个 zen 5 核心 256 线程 512 mb 缓存)

100-000001341 -12 ccd 1 iod(96 个 zen 5 核心 192 线程 384 mb 缓存)

100-000001247 -8 ccd 1 iod(64 个 zen 5 核心 128 线程 256 mb 缓存)

100-000001342 -8 ccd 1 iod(64 个 zen 5 核心 128 线程 256 mb 缓存)

100-000001249 -2 ccd 1 iod(32 个 zen 5c 核心 64 线程 64 mb 缓存)

相对于 zen 5 ccd,每个 zen 5c ccd 可提供最多 16 个核心和 32 mb 的 l3 缓存,再加上6 个计算芯片,总共可实现 192 个物理核心和 256 个逻辑线程,但 l3 缓存仅为 384 mb,并将保留与其他芯片相同的 i / o 模块。

与基于 zen 4c 核心的 bergamo 系列 cpu 相比,采用 zen 5c 核心的 turin 芯片核心和线程数将增加 50%(192/384 对 128/256),缓存数也将增加 50%(384 mb 对与 256 mb)。

amd 已确认基于 zen 5 架构的都灵 cpu 将于 2024 年推出,并将带来更强的单位功耗性能,从而对抗英特尔新一代的 granite rapids xeon 芯片。

编辑:齐少恒

相关热词搜索: